| Access |

| File | Description | Size | Format | | | | 330 B | HTML | | Copyrighted to the author. Reproduction is prohibited without the author’s prior written consent. | Cited By CountsOnline attention, usage metrics, similar items. - A 12-Bit, 300-MS/s Single-Channel Pipelined-SAR ADC With an Open-Loop MDAC Author(s): Wu, Chao ECE; Yuan, Jie 2019

- On the design of energy-efficient incremental delta-sigma ADCs Author(s): Mohamad, Saqib ECE 2019

- Digitally Calibrated 768-kS/s 10-b Minimum-Size SAR ADC Array With Dithering Author(s): Xu, Ruoyu; Liu, Bing; Yuan, Jie 2012

- Digital calibration of high-speed time-interleaved ADCs for high data rate communication system Author(s): Niu, Han 2022

- Fully Integrated Digital Controller IC for Buck Converter with a Differential-Sensing ADC Author(s): Chan, Man Pun; Mok, Philip K.T. 2008

A Power-Efficient SAR ADC with Optimized Timing-Redistribution Asynchronous SAR Logic in 40-nm CMOS- Published: 21 January 2021

- Volume 40 , pages 3125–3142, ( 2021 )

Cite this article - Mengying Hu 1 ,

- Jing Jin ORCID: orcid.org/0000-0003-3584-5559 1 ,

- Yuekang Guo 1 ,

- Xiaoming Liu 1 &

- Jianjun Zhou 1

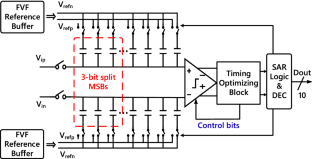

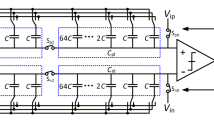

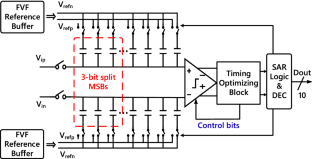

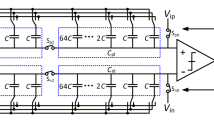

1100 Accesses 4 Citations Explore all metrics This paper presents a power-efficient successive-approximation register (SAR) analog-to-digital converter (ADC) with fast response reference buffer (RV-buffer). Several techniques are applied in the system design to improve the performance of the SAR ADC. A novel timing-redistribution SAR logic is proposed to balance the difference between required settling time for the most significant bit and the least significant bits (LSBs) in the digital-to-analog capacitor array, which reduces the incomplete settling error and releases the requirements on the RV-buffer to achieve lower power dissipation. The SAR ADC is fabricated in 40-nm CMOS technology occupying 0.13 mm \(^{2}\) area. At 1.1 V supply voltage and 80 MHz sampling frequency, the ADC achieves 50.7 dB SNDR, 69.5 dBc SFDR with a 1 MHz input at −8 dBFS. The total power consumption of the ADC is 2.99 mW, including the reference buffer power consumption of 2 mW. The Schreier FoM is 164.1 dB. This is a preview of subscription content, log in via an institution to check access. Access this articleSubscribe and save. - Get 10 units per month

- Download Article/Chapter or eBook

- 1 Unit = 1 Article or 1 Chapter

- Cancel anytime

Price includes VAT (Russian Federation) Instant access to the full article PDF. Rent this article via DeepDyve Institutional subscriptions  Similar content being viewed by others A 6-Bit Low Power SAR ADC High Performance SAR ADC with Mismatch Correction Latch and Improved Comparator Clock High Energy Efficiency and Linearity Switching Scheme Without Reset Energy for SAR ADCY. Cao, Y. Chen, Z. Ni, F. Ye, J. Ren, An 11b 80 ms/s SAR ADC with speed-enhanced SAR logic and high-linearity CDAC. In: 2018 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 18–21 (2018) Y. Chen, J. Wang, H. Hu, F. Ye, J. Ren, A 200 ms/s, 11 bit SAR-assisted pipeline ADC with bias-enhanced ring amplifier. In: 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4 (2017) Y. Chen, X. Zhu, H. Tamura, M. Kibune, Y. Tomita, T. Hamada, M. Yoshioka, K. Ishikawa, T. Takayama, J. Ogawa, S. Tsukamoto, T. Kuroda, Split capacitor DAC mismatch calibration in successive approximation ADC. In: 2009 IEEE Custom Integrated Circuits Conference, pp. 279–282 (2009) Y. Chung, C. Yen, An 11-bit 100-ms/s subranged-SAR ADC in 65-nm cmos. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 25 (12), 3434–3443 (2017) Article Google Scholar Y. Chung, C. Yen, P. Tsai, B. Chen, A 12-bit 40-ms/s SAR ADC with a fast-binary-window DAC switching scheme. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26 (10), 1989–1998 (2018) B.P. Ginsburg, A.P. Chandrakasan, 500-ms/s 5-bit ADC in 65-nm CMOS with split capacitor array DAC. IEEE J. Solid-State Circuits 42 (4), 739–747 (2007) P. Harikumar, J.J. Wikner, Design of a reference voltage buffer for a 10-bit 50 ms/s SAR ADC in 65 nm CMOS. In: 2015 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 249–252 (2015) M. Hesener, T. Eicher, A. Hanneberg, D. Herbison, F. Kuttner, H. Wenske, A 14b 40 ms/s redundant SAR ADC with 480 mhz clock in 0.13 pm CMOS. In: 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, pp. 248–600 (2007) C. Hsu, S. Chang, C. Huang, L. Chang, Y. Shyu, C. Hou, H. Tseng, C. Kung, H. Hu, A 12-b 40-ms/s calibration-free SAR ADC. IEEE Trans. Circuits Syst. I: Regular Papers 65 (3), 881–890 (2018) Y. Hu, A. Liu, B. Li, Z. Wu, Closed-loop charge recycling switching scheme for SAR ADC. Electron. Lett. 53 (2), 66–68 (2017) G. Huang, S. Chang, Y. Lin, C. Liu, C. Huang, A 10b 200 ms/s 0.82 mw SAR ADC in 40 nm CMOS. In: 2013 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 289–292 (2013) J.E. Kim, T. Yoo, K. Baek, T.T. Kim, Balanced sampling switch for high linearity and a wide temperature range in low power SAR ADCs. Electron. Lett. 55 (24), 1273–1275 (2019) D. Li, Z. Zhu, R. Ding, Y. Yang, A 1.4-mw 10-bit 150-ms/s SAR ADC with nonbinary split capacitive DAC in 65-nm CMOS. IEEE Trans. Circuits and Syst. II: Exp. Br. 65 (11), 1524–1528 (2018) W. Li, F. Li, J. Liu, H. Li, Z. Wang, A 13-bit 160 ms/s pipelined subranging-SAR ADC with low-offset dynamic comparator. In: 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 225–228 (2017) C. Liu, S. Chang, G. Huang, Y. Lin, A 10-bit 50-ms/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45 (4), 731–740 (2010) C. Liu, S. Chang, G. Huang, Y. Lin, C. Huang, C. Huang, L. Bu, C. Tsai, A 10b 100 ms/s 1.13 mw SAR ADC with binary-scaled error compensation. In: 2010 IEEE International Solid-State Circuits Conference—(ISSCC), pp. 386–387 (2010) C. Liu, C. Kuo, Y. Lin, A 10 bit 320 ms/s low-cost SAR ADC for IEEE 802.11ac applications in 20 nm CMOS. IEEE J. Solid-State Circuits 50 (11), 2645–2654 (2015) M. Liu, A. van Roermund, P. Harpe, A 7.1fj/conv.-step 88 db-sfdr 12b SAR ADC with energy-efficient swap-to-reset. In: ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, pp. 409–412 (2016) M. Liu, A.H.M. van Roermund, P. Harpe, A 7.1-fj/conversion-step 88-db SFDR SAR ADC with energy-free swap to reset. IEEE J Solid-State Circuits 52 (11), 2979–2990 (2017) W. Liu, P. Huang, Y. Chiu, A 12b 22.5/45 ms/s 3.0 mw 0.059 mm2 CMOS SAR ADC achieving over 90 db SFDR. In: 2010 IEEE International Solid-State Circuits Conference-(ISSCC), pp. 380–381 (2010) M. Akbari, O. Hashemipour, F. Khateb, F. Moradi, An energy-efficient DAC switching algorithm based on charge recycling method for SAR ADCs. Microelectron. J. 82 , 29–35 (2018) M. Akbari, O. Hashemipour, M. Nazari, F. Moradi, A charge sharing-based switching scheme for SAR ADCs. Int. J. Circuit Theory Appl. 47 (7), 1188–1198 (2019) T. Miki, T. Morie, K. Matsukawa, Y. Bando, T. Okumoto, K. Obata, S. Sakiyama, S. Dosho, A 4.2 mw 50 ms/s 13 bit CMOS SAR ADC with SNR and SFDR enhancement techniques. IEEE J. Solid-State Circuits 50 (6), 1372–1381 (2015) C. Park, T. Chen, K. Noh, D. Zhou, S. Prakash, M.N. Alizadeh, A.I. Karsilayan, D. Chen, R.L. Geiger, J. Silva-Martinez, A 12-bit 125-ms/s 25-bit/cycle SAR-based pipeline ADC employing a self-biased gain boosting amplifier. IEEE Trans. Circuits Syst. I: Regular Pap. 67 , 1–12 (2020) Article MathSciNet Google Scholar J. Park, D. Kim, T. An, M. Kim, G. Ahn, S. Lee, 12 b 50 ms/s 0.18 \(\mu \) m CMOS SAR ADC based on highly linear C-R hybrid DAC. Electron. Lett. 56 (3), 119–121 (2020) Y. Roh, D. Chang, S. Ryu, A 40-nm cmos 12b 120-ms/s nonbinary SAR-assisted SAR ADC with double clock-rate coarse decision. IEEE Trans. Circuits Syst. II: Exp. Br. 67 (12), 1 (2020) Y. Shen, Z. Zhu, S. Liu, Y. Yang, A reconfigurable 10-to-12-b 80-to-20-ms/s bandwidth scalable SAR ADC. IEEE Trans. Circuits Syst. I: Regular Pap. 65 (1), 51–60 (2018) L. Sun, B. Li, A.K.Y. Wong, W.T. Ng, K.P. Pun, A charge recycling sar adc with a LSB-down switching scheme. IEEE Trans. Circuits Syst. I: Regular Pap. 62 (2), 356–365 (2015) W. Tseng, W. Lee, C. Huang, P. Chiu, A 12-bit 104 ms/s sar adc in 28 nm cmos for digitally-assisted wireless transmitters. IEEE J. Solid-State Circuits 51 (10), 2222–2231 (2016) W. Tung, S. Huang, An energy-efficient 11-bit 10-ms/s SAR ADC with monotonie switching split capacitor array. In: 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5 (2018) D. Xu, H. Jiang, L. Qiu, X. Yu, J. Wang, Z. Zhang, C. Zhu, S. Xu, A linearity-enhanced 10-bit 160-ms/s SAR ADC with low-noise comparator technique. IEEE Trans Very Large Scale Integr (VLSI) Syst 27 (9), 1990–1997 (2019) J. Xue, H. Ghaedrahmati, J. Jin, A 10-bit 160ms/s SAR ADC with fast-response reference voltage buffer. In: 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), pp. 1–3 (2018) T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. II: Exp. Br. 65 (1), 41–45 (2018) H. Zhang, J. Sun, J. Zhang, R. Zhang, A. ChanCarusone, A low-power pipelined-SAR ADC using boosted bucket-brigade device for residue charge processing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26 (9), 1763–1776 (2018) M. Zhang, K. Noh, X. Fan, E. Sánchez-Sinencio, A 0.8–1.2 v 10–50 ms/s 13-bit subranging pipelined-sar adc using a temperature-insensitive time-based amplifier. IEEE J. Solid-State Circuits 52 (11), 2991–3005 (2017) Y. Zhu, C. Chan, U. Chio, S. Sin, U. Seng-Pan, R.P. Martins, F. Maloberti, A 10-bit 100-ms/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45 (6), 1111–1121 (2010) Download references AcknowledgementsWe would like to thank the Chinese National Nature Science Foundation (No. 61974092) for funding this research. Chinese National Nature Science Foundation (No. 61974092) Author informationAuthors and affiliations. Center for Analog/RF Integrated Circuits (CARFIC), Department of Micro/Nano Electronics, Shanghai Jiao Tong University, Shanghai, 200240, China Mengying Hu, Jing Jin, Yuekang Guo, Xiaoming Liu & Jianjun Zhou You can also search for this author in PubMed Google Scholar  Corresponding authorCorrespondence to Jing Jin . Ethics declarationsConflicts of interest/competing interests. No conflicts or interests with any authorities or person Availability of data and materialAll data used in this essay are collected by the authors mentioned in the essay without other sources Code availabilityNo software application or custom code are utilized in the research process Additional informationPublisher's note. Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations. Rights and permissionsReprints and permissions About this articleHu, M., Jin, J., Guo, Y. et al. A Power-Efficient SAR ADC with Optimized Timing-Redistribution Asynchronous SAR Logic in 40-nm CMOS. Circuits Syst Signal Process 40 , 3125–3142 (2021). https://doi.org/10.1007/s00034-020-01643-z Download citation Received : 03 August 2020 Revised : 23 December 2020 Accepted : 24 December 2020 Published : 21 January 2021 Issue Date : July 2021 DOI : https://doi.org/10.1007/s00034-020-01643-z Share this articleAnyone you share the following link with will be able to read this content: Sorry, a shareable link is not currently available for this article. Provided by the Springer Nature SharedIt content-sharing initiative - Timing-optimized SAR logic

- Low power consumption

- Find a journal

- Publish with us

- Track your research

A 17 MS/s SAR ADC with energy-efficient switching strategyNew citation alert added. This alert has been successfully added and will be sent to: You will be notified whenever a record that you have chosen has been cited. To manage your alert preferences, click on the button below. New Citation Alert!Please log in to your account Information & ContributorsBibliometrics & citations, view options. - Huang Y Huang L Wu J (2021) An energy-efficient switching scheme based on the improved semi-resting DAC structure and floating-capacitor technique for SAR ADC Analog Integrated Circuits and Signal Processing 10.1007/s10470-021-01910-2 108 :3 (679-687) Online publication date: 1-Sep-2021 https://dl.acm.org/doi/10.1007/s10470-021-01910-2

- Ghoshal P Dey C Sen S (2021) Realization of an ultra low power and area efficient SC SAR ADC architecture using single and two step reset methods Microsystem Technologies 10.1007/s00542-020-05118-8 27 :9 (3571-3577) Online publication date: 1-Sep-2021 https://dl.acm.org/doi/10.1007/s00542-020-05118-8

- Li J Li X Huang L Wu J (2020) An energy-efficient switching scheme with low common-mode voltage variation and no-capacitor-splitting DAC for SAR ADC Analog Integrated Circuits and Signal Processing 10.1007/s10470-020-01661-6 104 :1 (93-101) Online publication date: 11-May-2020 https://dl.acm.org/doi/10.1007/s10470-020-01661-6

RecommendationsA 3.66 μw 12-bit 1 ms/s sar adc with mismatch and offset foreground calibration. This paper presents a 12-bit 1 MS/s successive approximation register (SAR) analog-to-digital converter (ADC) with foreground calibration for digital-to-analog converter (DAC) mismatch and comparator static offset errors. The proposed ... A 15-Bit 85 MS/s Hybrid Flash-SAR ADC in 90-nm CMOSA 15-bit, 85 MS/s hybrid flash-SAR ADC is presented. The proposed design combines modified tri-level switching technique with split capacitor technique to improve the power efficiency and sampling rate of the SAR block. The sampling switch was designed ... A 1.2 V 8-bit 1 MS/s SAR ADC with Res---Cap segment DAC for temperature sensor in LTEA 1.2 V 8-bit single ended successive approximation register analog-to-digital converter (ADC) for long term evolution (LTE) system is implemented. A novel 5-bit resistor and 3-bit capacitor segment digital-to-analog converter is used to minimize the ... InformationPublished in. Kluwer Academic Publishers United States Publication HistoryAuthor tags. - High-resolution

- Research-article

ContributorsOther metrics, bibliometrics, article metrics. - 3 Total Citations View Citations

- 0 Total Downloads

- Downloads (Last 12 months) 0

- Downloads (Last 6 weeks) 0

View optionsLogin options. Check if you have access through your login credentials or your institution to get full access on this article. Full AccessShare this publication link. Copying failed. Share on social mediaAffiliations, export citations. - Please download or close your previous search result export first before starting a new bulk export. Preview is not available. By clicking download, a status dialog will open to start the export process. The process may take a few minutes but once it finishes a file will be downloadable from your browser. You may continue to browse the DL while the export process is in progress. Download

- Download citation

- Copy citation

We are preparing your search results for download ... We will inform you here when the file is ready. Your file of search results citations is now ready. Your search export query has expired. Please try again. IEEE Account- Change Username/Password

- Update Address

Purchase Details- Payment Options

- Order History

- View Purchased Documents

Profile Information- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions. InformationInitiativesYou are accessing a machine-readable page. In order to be human-readable, please install an RSS reader. All articles published by MDPI are made immediately available worldwide under an open access license. No special permission is required to reuse all or part of the article published by MDPI, including figures and tables. For articles published under an open access Creative Common CC BY license, any part of the article may be reused without permission provided that the original article is clearly cited. For more information, please refer to https://www.mdpi.com/openaccess . Feature papers represent the most advanced research with significant potential for high impact in the field. A Feature Paper should be a substantial original Article that involves several techniques or approaches, provides an outlook for future research directions and describes possible research applications. Feature papers are submitted upon individual invitation or recommendation by the scientific editors and must receive positive feedback from the reviewers. Editor’s Choice articles are based on recommendations by the scientific editors of MDPI journals from around the world. Editors select a small number of articles recently published in the journal that they believe will be particularly interesting to readers, or important in the respective research area. The aim is to provide a snapshot of some of the most exciting work published in the various research areas of the journal. Original Submission Date Received: . - Active Journals

- Find a Journal

- Proceedings Series

- For Authors

- For Reviewers

- For Editors

- For Librarians

- For Publishers

- For Societies

- For Conference Organizers

- Open Access Policy

- Institutional Open Access Program

- Special Issues Guidelines

- Editorial Process

- Research and Publication Ethics

- Article Processing Charges

- Testimonials

- Preprints.org

- SciProfiles

- Encyclopedia

Article Menu - Subscribe SciFeed

- Recommended Articles

- Google Scholar

- on Google Scholar

- Table of Contents

Find support for a specific problem in the support section of our website. Please let us know what you think of our products and services. Visit our dedicated information section to learn more about MDPI. JSmol ViewerAnalysis of the second-order ns sar adc performance enhancement based on active gain.  1. Introduction2. mathematical analysis of previous second-order fully-passive ns sar adc, 3. the proposed second-order ns sar adc, 3.1. the second-order ns sar adc based on active gain, 3.2. improved second-order ns sar adc based on active gain, 3.3. the values of a and δt/τ, 3.4. improved sampling speed, 3.5. kickback noise, 4. performance comparison, 5. conclusions, author contributions, data availability statement, conflicts of interest. - Elzakker, M.v.; Tuijl, E.v.; Geraedts, P.; Schinkel, D.; Klumperink, E.A.M.; Nauta, B. A 10-bit Charge-Redistribution ADC Consuming 1.9 μW at 1 MS/s. IEEE J. Solid-State Circuits 2010 , 45 , 1007–1015. [ Google Scholar ] [ CrossRef ]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z.; Huang, C.M. A 1V 11fJ/conversion-step 10bit 10MS/s asynchronous SAR ADC in 0.18µm CMOS. In Proceedings of the 2010 Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010; pp. 241–242. [ Google Scholar ]

- Shen, Y.; Tang, X.; Shen, L.; Zhao, W.; Xin, X.; Liu, S.; Zhu, Z.; Sathe, V.S.; Sun, N. A 10-bit 120-MS/s SAR ADC With Reference Ripple Cancellation Technique. IEEE J. Solid-State Circuits 2020 , 55 , 680–692. [ Google Scholar ] [ CrossRef ]

- Xu, D.G.; Xu, K.K.; Xu, S.L.; Liu, L.; Liu, T. A System-Level Correction SAR ADC with Noise-Tolerant Technique. J. Circuits Syst. Comput. 2018 , 27 , 1850202. [ Google Scholar ] [ CrossRef ]

- Obata, K.; Matsukawa, K.; Miki, T.; Tsukamoto, Y.; Sushihara, K. A 97.99 dB SNDR, 2 kHz BW, 37.1 µW noise-shaping SAR ADC with dynamic element matching and modulation dither effect. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [ Google Scholar ]

- Shu, Y.S.; Kuo, L.T.; Lo, T.Y. An Oversampling SAR ADC With DAC Mismatch Error Shaping Achieving 105 dB SFDR and 101 dB SNDR Over 1 kHz BW in 55 nm CMOS. IEEE J. Solid-State Circuits 2016 , 51 , 2928–2940. [ Google Scholar ] [ CrossRef ]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 2nd order fully-passive noise-shaping SAR ADC with embedded passive gain. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 309–312. [ Google Scholar ]

- Li, S.; Qiao, B.; Gandara, M.; Pan, D.Z.; Sun, N. A 13-ENOB Second-Order Noise-Shaping SAR ADC Realizing Optimized NTF Zeros Using the Error-Feedback Structure. IEEE J. Solid-State Circuits 2018 , 53 , 3484–3496. [ Google Scholar ] [ CrossRef ]

- Fredenburg, J.A.; Flynn, M.P. A 90-MS/s 11-MHz-Bandwidth 62-dB SNDR Noise-Shaping SAR ADC. IEEE J. Solid-State Circuits 2012 , 47 , 2898–2904. [ Google Scholar ] [ CrossRef ]

- Guo, W.; Zhuang, H.; Sun, N. A 13b-ENOB 173dB-FoM 2nd-order NS SAR ADC with passive integrators. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C236–C237. [ Google Scholar ]

- Miki, T.; Morie, T.; Matsukawa, K.; Bando, Y.; Okumoto, T.; Obata, K.; Sakiyama, S.; Dosho, S. A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC With SNR and SFDR Enhancement Techniques. IEEE J. Solid-State Circuits 2015 , 50 , 1372–1381. [ Google Scholar ] [ CrossRef ]

- Kuo, H.L.; Lu, C.W.; Chen, P. An 18.39 fJ/Conversion-Step 1-MS/s 12-bit SAR ADC With Non-Binary Multiple-LSB-Redundant and Non-Integer-and-Split-Capacitor DAC. IEEE Access 2021 , 9 , 5651–5669. [ Google Scholar ] [ CrossRef ]

- Jiao, Z.; Luo, H.; Zhang, J.; Wang, X.; Chen, L.; Zhang, H. An 84dB-SNDR 1-0 Quasi-MASH NS SAR with LSB Repeating and 12-bit Bridge-Crossing Segmented CDAC. In Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC), San Antonio, TX, USA, 23–26 April 2023; pp. 1–2. [ Google Scholar ]

- Harpe, P.; Cantatore, E.; Roermund, A.v. A 10b/12b 40 kS/s SAR ADC with Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step. IEEE J. Solid-State Circuits 2013 , 48 , 3011–3018. [ Google Scholar ] [ CrossRef ]

- Hwang, Y.H.; Song, Y.; Park, J.E.; Jeong, D.K. A Fully Passive Noise-Shaping SAR ADC Utilizing Last-Bit Majority Voting and Cyclic Dynamic Element Matching Techniques. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022 , 30 , 1381–1390. [ Google Scholar ] [ CrossRef ]

- Zhuang, H.; Guo, W.; Liu, J.; Tang, H.; Zhu, Z.; Chen, L.; Sun, N. A Second-Order Noise-Shaping SAR ADC with Passive Integrator and Tri-Level Voting. IEEE J. Solid-State Circuits 2019 , 54 , 1636–1647. [ Google Scholar ] [ CrossRef ]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C64–C65. [ Google Scholar ]

- Guo, W.; Sun, N. A 12b-ENOB 61µW noise-shaping SAR ADC with a passive integrator. In Proceedings of the ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, Lausanne, Switzerland, 12–15 September 2016; pp. 405–408. [ Google Scholar ]

- Kandala, M.; Sekar, R.; Chenglong, Z.; Haibo, W. A low power charge-redistribution ADC with reduced capacitor array. In Proceedings of the 2010 11th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, USA, 22–24 March 2010; pp. 44–48. [ Google Scholar ]

- Zhan, M.; Jie, L.; Tang, X.; Sun, N. A 0.004mm 2 200MS/S Pipelined SAR ADC with kT/C Noise Cancellation and Robust Ring-Amp. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 164–166. [ Google Scholar ]

- Liu, J.; Tang, X.; Zhao, W.; Shen, L.; Sun, N. A 13-bit 0.005-mm 2 40-MS/s SAR ADC With kT/C Noise Cancellation. IEEE J. Solid-State Circuits 2020 , 55 , 3260–3270. [ Google Scholar ] [ CrossRef ]

- Li, H.; Youssef, M.; Shen, Y.; Cantatore, E.; Harpe, P. Analysis of the Sampling Noise Cancellation Technique in a Track-and-Hold Amplifier. In Proceedings of the 2021 28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Dubai, United Arab Emirates, 28 November–1 December 2021; pp. 1–5. [ Google Scholar ]

- Xu, K. Silicon electro-optic micro-modulator fabricated in standard CMOS technology as components for all silicon monolithic integrated optoelectronic systems*. J. Micromech. Microeng. 2021 , 31 , 054001. [ Google Scholar ] [ CrossRef ]

- Figueiredo, P.M.; Vital, J.C. Kickback noise reduction techniques for CMOS latched comparators. IEEE Trans. Circuits Syst. II Express Briefs 2006 , 53 , 541–545. [ Google Scholar ] [ CrossRef ]

- Razavi, B. The StrongARM Latch [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2015 , 7 , 12–17. [ Google Scholar ] [ CrossRef ]

- Wu, K.J.; Li, J.; Wang, X.Z.; Ning, N.; Xu, K.K.; Yu, Q. Switching sequence optimization for gradient errors compensation in the current-steering DAC design. Microelectron. J. 2020 , 95 , 104662. [ Google Scholar ] [ CrossRef ]

Click here to enlarge figure | Architecture | Second-Order Fully-Passive NS SAR | NS SAR Based on Active Gain | Improved NS SAR Based on Activegain |

|---|

| C | large | medium | small | | ADC Input Cap | | | | | kT/C Suppressed? | × | √ | √ | | Comparator Noise Suppressed? | √ | √ | √ | | Extra Cycles? | √ | × | × | | Static Power | × | √ | √ | | The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

Share and CiteJia, S.; Ye, T.; Xiao, S. Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain. Electronics 2024 , 13 , 3400. https://doi.org/10.3390/electronics13173400 Jia S, Ye T, Xiao S. Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain. Electronics . 2024; 13(17):3400. https://doi.org/10.3390/electronics13173400 Jia, Shichao, Tianchun Ye, and Shimao Xiao. 2024. "Analysis of the Second-Order NS SAR ADC Performance Enhancement Based on Active Gain" Electronics 13, no. 17: 3400. https://doi.org/10.3390/electronics13173400 Article MetricsArticle access statistics, further information, mdpi initiatives, follow mdpi.  Subscribe to receive issue release notifications and newsletters from MDPI journals  |

IMAGES

VIDEO

COMMENTS

AR ADC was designed and fabricated as a proof of concept for these design techniques.Finally, we investigated the concept of SAR-pipelining as a viable option to realize moderate. o high resolution (> 65 dB SNDR), high-speed (> 150 MS/s), low energy A/D converters. A mod.

The top-level block diagram of the asynchronous SAR ADC is shown below, along with the timing diagram of the important signals. ... "A study of SAR ADC and implementation of 10-bit asynchronous design," M.S. Thesis, Department of Electrical and Computer Engineering, University of Texas at Austin, 2013. [2] P. J. A. Harpe et al., "A 26 uW 8 bit ...

In this work, an asynchronous implementation of the SAR ADC was employed. Typical synchronous implementations [] make use of two synchronized clock sources, one to control the data sampling (the sampling clock) and other to control the converter iterations (the SAR iteration clock).On the other hand, asynchronous SAR ADCs [7, 8] require only one clock signal to control the sampling.

step FoM. This ADC achieves the best FoM of any ADCs with greater than 10b ENOB and 10MS/s sampling rate. Thesis Supervisor: Duane S. Boning Title: Professor of Electrical Engineering and Computer Science Thesis Supervisor: Hae-Seung Lee Title: Professor of Electrical Engineering and Computer Science 3

The proposed ADC is aimed at a tactile sensor application, requiring a low-noise and low-power solution. In addition, it should have high SNDR to detect even the weakest signals with precision. This thesis presents a 12-bit 400 kS/s SAR ADC implemented in a 180 nm CMOS technology for such a task.

ADC. ThesisPDF Available. Masters Dissertation: Design of a low-power 10-bit 12-MS/s asynchronous SAR ADC. September 2020. DOI: 10.11606/D.18.2020.tde-16122021-162821. Thesis for: Master of ...

A 150-MS/s 8-bit LU-SAR ADC is fabricated in a 130-nm CMOS technology to validate the concept. The measured result shows that the calibration improves the SNDR from 33.7-dB to 42.9-dB. The ADC consumes 640 μW from a 1.2 V supply with a Figure-of-Merit (FoM) of 37.5-fJ/conv-step. Moreover, the bit-wise impact of comparator noise is studied for ...

This paper presents a cutting-edge 1.2V 10-bit asynchronous Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) meticulously designed and simulated in the advanced 18 nm FinFET CMOS technology. This asynchronous SAR ADC system consists of an internal-clock generator, switching unit, fully differential pair of capacitive Digital-to-Analog Converter (DAC), a dynamic ...

Key words: SAR ADC, asynchronous SAR logic, bootstrapped switch, dynamic comparator, LHAASO, WCDA PACS: 84.30.-r, 07.05.Hd 1 Introduction The Large High Altitude Air Shower Observatory (LHAASO) project has been proposed for high energy gamma ray and cosmic ray detection [1-3]. One of the major components is the Water Cherenkov Detector Array

This paper introduces an innovative concept centered on developing an 8-bit Asynchronous Successive Approximation Register (SAR) Analog to Digital Converter (ADC) utilizing state-of-the-art 18nm FinFET technology. This advanced asynchronous SAR system encompasses multiple crucial components, including a precisely engineered internal clock generator, a high-performance bootstrapped sample and ...

A low power 12-bit, 20 MS/s asynchronously controlled successive approximation register (SAR) analog-to-digital converter (ADC) to be used in wireless access for vehicular environment (WAVE) intelligent transportation system (ITS) sensor based application is presented in this paper. To optimize the architecture with respect to power consumption and performance, several techniques are proposed.

D. Zhang, Design of Ultra-Low-Power Analog-to-Digital Converters, Linköping: PhD Thesis, 2012. Google Scholar; A. M. Abo and P. R. Gray, "A 1.5-V, ... Design of a low power 10-bit 12MS/s asynchronous SAR ADC in 65nm CMOS. Hardware. Integrated circuits. Very large scale integration design. Analog and mixed-signal circuits.

Successive approximation register (SAR) analog-to-digital converters (ADCs) are widely used in biomedical and portable/wearable electronic systems due to their excellent power efficiency. However, both the design and the optimization of high-performance SAR ADCs are time consuming, even for well-experienced circuit designers. For system designers, it is also hard to quickly evaluate the ...

1.1 Thesis organization 3 2. High-speed sampling 4 2.1 Track-and-hold circuits 4 ... asynchronous SAR ADC with 400mV input swing and 1.05V supply 34 3.8 Waveform of a classic asynchronous SAR ADC in the scenario that (a) a meta-stability event does not cause a sparkle-code and (b) a meta-stability event caused a sparkle-code 35 ...

A 26 $\mu$ W 8 bit 10 MS/s Asynchronous SAR ADC for Low Energy Radios. The fully dynamic design, which is optimized for low-leakage, leads to a standby power consumption of 6 nW and the energy efficiency of this converter can be maintained down to very low sampling rates.

A loop-unrolled asynchronous SAR ADC is used to speed up the sub-ADC further. This architecture uses n comparators for an n-bit ADC. The outputs of the comparators can be directly given to the SAR DAC array without any extra logic and there is also no need for the comparators to do the reset within one conversion period. ... Thesis (Ph.D ...

A design of low-power 10-bit 1 MS/s asynchronous successive approximation register analog-to-digital converter (SAR ADC) is presented in this paper. To improve the linearity of the digital-to-analog converter (DAC) and energy efficiency, a common mode-based monotonic charge recovery (CMMC) switching technique is proposed. The proposed switching technique consumes only 63.75 CVREF2 switching ...

First, a 9-bit 16-way time-interleaved SAR ADC core including decoupling capacitor and voltage references are fully generated by the generator. It works at sampling rate 10GS/s and simulated SNDR is 37.6 dB at Nyquist frequency. In order to set the con guration bits and read out quantized result.

This paper presents a comparison between a Itl-bit asynchronous SAR (ASAR) ADC and a 10-bit synchronous SAR (SSAR) ADC, both designed and simulated in a 22-nm FDSOI CMOS process. To further support the simulation results, the ASAR ADC has also been fabricated and measurements are pre-sented. As opposed to the abrupt SNDR collapse in the SSAR ADC, the SNDR of the ASAR ADC shows a more graceful ...

Low-power, high-speed ADCs are in great needs. New opportunities and breakthroughs are expected in accelerated rate. Asynchronous SAR ADC architecture provides power efficient platform for achieving this goal. The record high-speed (90GS/s) ADC also leverages this topology.

This paper presents a power-efficient successive-approximation register (SAR) analog-to-digital converter (ADC) with fast response reference buffer (RV-buffer). Several techniques are applied in the system design to improve the performance of the SAR ADC. A novel timing-redistribution SAR logic is proposed to balance the difference between required settling time for the most significant bit ...

This work presents the design and implementation of a low power successive approximation register analog-to-digital converter (SAR ADC) in a 65nm CMOS technology, suitable for low power frontend of wireless receivers with a flexible sampling rate up to 12 MS/s.

A study of SAR ADC and implementation of 10-Bit asynchronous design. A thesis submitted to the University of Texas at Austin for the degree of Master of Science in Engineering. ... Wen, J. Y., Chang, P. H., Huang, J. F., & Lai, W. C. (2015). Chip design of a 12-bit 5MS/s fully differential SAR ADC with resistor-capacitor array DAC technique for ...

In this paper 8 bit SAR ADC with input voltage of 1.2V has been designed. The schematic diagram of different sub blocks has been implemented in Cadence Virtuoso using 180nm technology. Comparator was designed so that it remains in saturation for proper operation and was implemented using differential amplifier. The comparator is the main power consuming block, so most of our effort was focused ...

This paper presents a novel second-order passive noise shaping (NS) successive approximation register (SAR) analog-to-digital converter (ADC) based on active gain. The proposed scheme achieves a further improvement in the signal-to-noise ratio (SNR) of the proposed NS SAR ADC by reducing the kT/C noise and the conversion rate. After having presented the conversion principle, the theoretical ...