Verilog Blocking & Non-Blocking

Blocking assignment statements are assigned using = and are executed one after the other in a procedural block. However, this will not prevent execution of statments that run in a parallel block.

Note that there are two initial blocks which are executed in parallel when simulation starts. Statements are executed sequentially in each block and both blocks finish at time 0ns. To be more specific, variable a gets assigned first, followed by the display statement which is then followed by all other statements. This is visible in the output where variable b and c are 8'hxx in the first display statement. This is because variable b and c assignments have not been executed yet when the first $display is called.

In the next example, we'll add a few delays into the same set of statements to see how it behaves.

Non-blocking

Non-blocking assignment allows assignments to be scheduled without blocking the execution of following statements and is specified by a symbol. It's interesting to note that the same symbol is used as a relational operator in expressions, and as an assignment operator in the context of a non-blocking assignment. If we take the first example from above, replace all = symobls with a non-blocking assignment operator , we'll see some difference in the output.

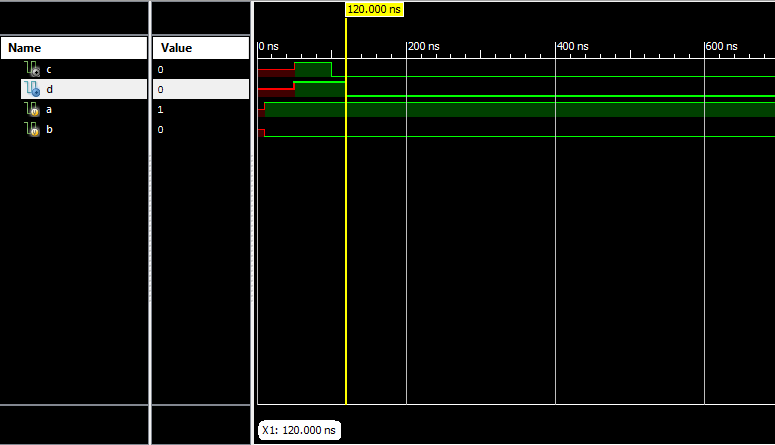

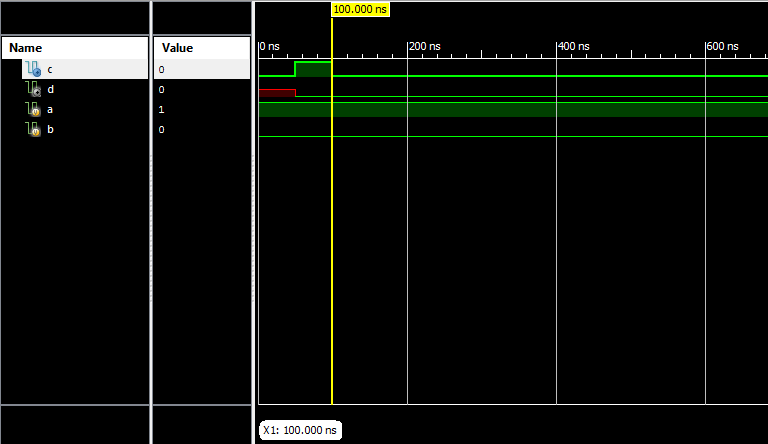

See that all the $display statements printed 'h'x . The reason for this behavior lies in the way non-blocking assignments are executed. The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step.

So, if we break down the execution flow of the above example we'll get something like what's shown below.

Next, let's use the second example and replace all blocking statements into non-blocking.

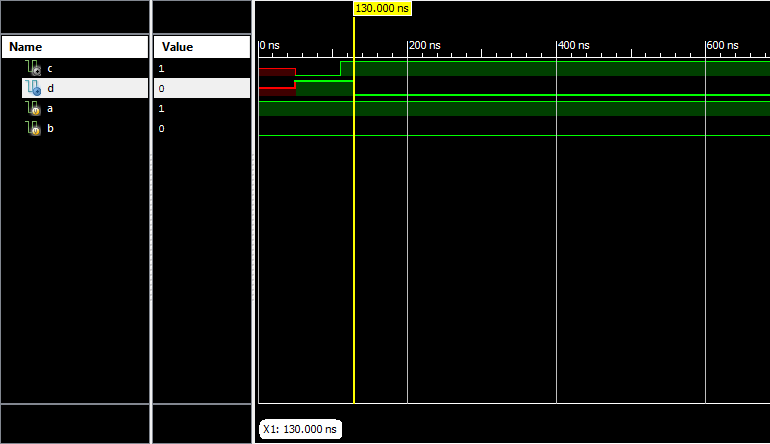

Once again we can see that the output is different than what we got before.

If we break down the execution flow we'll get something like what's shown below.

Blocking vs. Nonblocking in Verilog

The concept of Blocking vs. Nonblocking signal assignments is a unique one to hardware description languages. The main reason to use either Blocking or Nonblocking assignments is to generate either combinational or sequential logic. In software, all assignments work one at a time. So for example in the C code below:

The second line is only allowed to be executed once the first line is complete. Although you probably didn’t know it, this is an example of a blocking assignment. One assignment blocks the next from executing until it is done. In a hardware description language such as Verilog there is logic that can execute concurrently or at the same time as opposed to one-line-at-a-time and there needs to be a way to tell which logic is which.

<= Nonblocking Assignment

= Blocking Assignment

The always block in the Verilog code above uses the Nonblocking Assignment, which means that it will take 3 clock cycles for the value 1 to propagate from r_Test_1 to r_Test_3. Now consider this code:

See the difference? In the always block above, the Blocking Assignment is used. In this example, the value 1 will immediately propagate to r_Test_3 . The Blocking assignment immediately takes the value in the right-hand-side and assigns it to the left hand side. Here’s a good rule of thumb for Verilog:

In Verilog, if you want to create sequential logic use a clocked always block with Nonblocking assignments. If you want to create combinational logic use an always block with Blocking assignments. Try not to mix the two in the same always block.

Nonblocking and Blocking Assignments can be mixed in the same always block. However you must be careful when doing this! It’s actually up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a Flip-Flop or not. If it is possible that the signal will be read before being assigned, the tools will infer sequential logic. If not, then the tools will generate combinational logic. For this reason it’s best just to separate your combinational and sequential code as much as possible.

One last point: you should also understand the semantics of Verilog. When talking about Blocking and Nonblocking Assignments we are referring to Assignments that are exclusively used in Procedures (always, initial, task, function). You are only allowed to assign the reg data type in procedures. This is different from a Continuous Assignment . Continuous Assignments are everything that’s not a Procedure, and only allow for updating the wire data type.

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

Embedded VLSI Research Hub

Blocking and Non-blocking Assignments in Verilog

Introduction to blocking and non-blocking assignments in verilog programming language.

Hello, fellow Verilog enthusiasts! In this blog post, I will introduce you to the concepts of Blocking and Non-blocking Assignments in

Blocking assignments, using the = operator, ensure sequential execution within procedural blocks, making them ideal for combinational logic. Non-blocking assignments, using the <= operator, allow for concurrent execution, which is essential for modeling sequential logic accurately. Understanding the differences between these assignments will help you write more efficient and accurate Verilog code. Let’s dive into the details of each type and see how they impact your designs!

What are Blocking and Non-blocking Assignments in Verilog Programming Language?

In Verilog, blocking and non-blocking assignments determine how variables receive values and manage the execution of statements within procedural blocks. These assignments play a crucial role in modeling and simulating digital circuits, ensuring that your designs perform as intended.

1. Blocking Assignments

Blocking assignments use the = operator and are characterized by their sequential execution within procedural blocks. This means that each assignment must complete before the subsequent statements can execute. They are suitable for modeling combinational logic, where the order of operations affects the outcome.

Characteristics of Blocking Assignments:

1. sequential execution:.

Each blocking assignment statement blocks or halts the execution of subsequent statements until it finishes. This ensures that operations occur in a specific sequence, which is crucial when the result of one operation is used in the next.

For example, if multiple calculations depend on the results of previous ones, blocking assignments ensure that these dependencies are respected.

2. Immediate Update:

The value of the variable is updated immediately after the assignment statement is executed. This immediate update is ideal for combinational logic, where the output should directly reflect changes in the input.

3. Combinational Logic:

Blocking assignments work best in combinational logic modeling, where outputs depend on current inputs without considering past states or clock edges.

In this example, a is assigned the result of b + c first. Only after this assignment is complete does the next statement execute, assigning d the result of a – e.

2. Non-Blocking Assignments

Non-blocking assignments use the <= operator and allow for concurrent execution of statements within the same procedural block. They schedule the updates to occur at the end of the current time step or clock cycle, enabling multiple assignments to happen simultaneously. This behavior is essential for modeling sequential logic, where the updates to variables occur at specific times, often driven by clock edges.

Characteristics of Non-Blocking Assignments:

1. concurrent execution:.

Non-blocking assignments do not block the execution of subsequent statements. All non-blocking assignments within the same procedural block are executed in parallel, but the actual updates to the variables occur at the end of the current time step or clock cycle.

This allows for a more natural representation of how hardware behaves, where multiple updates can occur simultaneously.

2. Deferred Update:

The value of the variable is not updated immediately. Instead, the assignment schedules the update to occur at the end of the time step, allowing other operations to proceed based on the old value before the update takes effect.

3. Sequential Logic:

Non-blocking assignments are ideal for modeling sequential circuits such as flip-flops and registers, where the value changes in sync with clock edges or specific events.

In this example, the value of a updates with b + c at the end of the clock cycle. Simultaneously, d updates with the value of a – e at the end of the cycle, reflecting the updated value of a .

Why we need Blocking and Non-blocking Assignments in Verilog Programming Language?

Blocking and non-blocking assignments are fundamental in Verilog for modeling different aspects of digital circuits. Blocking assignments are ideal for combinational logic and scenarios requiring sequential execution, providing immediate updates and simplifying code flow.

Non-blocking assignments are essential for modeling sequential logic, ensuring accurate timing and synchronization with clock edges, and preventing race conditions. By using these assignments appropriately, designers can create accurate, reliable, and efficient digital circuits.

Blocking assignments are essential when you need sequential execution of statements. They play a crucial role in:

1. Modeling Combinational Logic

Sequential Execution: Blocking assignments ensure that operations occur in a specified order, which is crucial when one operation’s result is needed for subsequent operations within the same procedural block.

Immediate Updates: Since blocking assignments update variables immediately, they are suitable for combinational logic where the output must reflect changes in input instantly.

2. Simplifying Code

Predictable Execution Flow: By ensuring that statements execute sequentially, blocking assignments simplify the reasoning about how values change within a procedural block, making the code easier to understand and debug.

3. Initializations in Testbenches

Setup and Initialization: In testbenches, blocking assignments are commonly used to set initial values for simulation variables, configure test conditions, or initialize registers and memories at the start of the simulation.

Non-blocking assignments are crucial for accurately modeling sequential logic and concurrent behavior in digital designs. They are necessary for:

1. Modeling Sequential Logic

Concurrent Execution: Non-blocking assignments enable parallel processing of multiple assignments, with updates occurring at the end of the time step or clock cycle. This is crucial for accurately modeling sequential circuits such as flip-flops, counters, and registers, where changes need synchronization with clock edges.

Avoiding Race Conditions: Non-blocking assignments defer updates to prevent race conditions and ensure consistent variable updates within a clock cycle.

2. Synchronizing with Clock Edges

Timing Accuracy: Use non-blocking assignments to model behavior that changes with clock edges, ensuring updates occur at specific times and reflect real hardware operation. This timing accuracy is critical for designing reliable and functional sequential circuits.

3. Improving Simulation Accuracy

Behavioral Consistency: In simulations, non-blocking assignments provide a more accurate representation of how hardware behaves by allowing the model to reflect the actual timing and synchronization of updates, which is essential for verifying and validating designs.

Example of Blocking and Non-blocking Assignments in Verilog Programming Language

Here are examples of blocking and non-blocking assignments in Verilog, illustrating their usage in different contexts:

1. Blocking Assignments Example

Blocking assignments use the = operator and are executed sequentially within a procedural block. They are typically used for combinational logic where the order of operations is important.

Explanation:

- The always @(*) block is sensitive to any changes in a, b, or c.

- The assignments a = 8’b00001111; and b = 8’b11110000; occur sequentially.

- result = a + b; uses the updated values of a and b because the previous assignments must complete before this statement executes.

2. Non-Blocking Assignments Example

Non-blocking assignments use the <= operator and allow for concurrent execution of statements within a procedural block. They model sequential logic and ensure updates occur at the end of the current time step or clock cycle.

- The always @(posedge clk or posedge reset) block is sensitive to positive edges of clk or reset.

- On each clock edge, temp <= data_in; schedules temp to be updated at the end of the clock cycle with the value of data_in.

- data_out <= temp; schedules data_out to be updated with the value of temp at the end of the same clock cycle.

- Both assignments occur concurrently, with updates deferred until the end of the clock cycle. This ensures that data_out receives the value of temp from the same clock cycle.

Blocking Assignments ( = ) are used for sequential execution within procedural blocks, making them suitable for combinational logic where immediate updates and specific execution order are required.

Non-Blocking Assignments ( <= ) are used for concurrent execution, which is essential for sequential logic where updates need to be synchronized with clock edges and occur at the end of a time step or clock cycle.

Advantages of Blocking and Non-blocking Assignments in Verilog Programming Language

Blocking and non-blocking assignments in Verilog each offer distinct advantages based on their usage contexts. Here’s a detailed look at the advantages of each:

1. Advantages of Blocking Assignments

1.1 sequential execution:.

Predictable Flow: Blocking assignments execute statements in a sequential order, ensuring that the outcome of one assignment is available for the next. This predictability simplifies debugging and understanding the flow of combinational logic.

1.2 Simplicity in Combinational Logic:

Straightforward Coding: For combinational logic where the order of operations is crucial, blocking assignments make it easier to express complex logic without dealing with concurrency issues.

1.3 Ease of Initialization:

Clear Initialization: Use blocking assignments to initialize values in simulations or testbenches. They provide a straightforward method for setting up initial conditions, which helps in ensuring that the simulation starts from a known state.

1.4 Immediate Updates:

Instant Results: Blocking assignments update variables immediately, making them well-suited for scenarios where you need immediate feedback, such as in combinational logic calculations.

2. Advantages of Non-Blocking Assignments

2.1 modeling sequential logic:.

Accurate Timing: Non-blocking assignments are essential for accurately modeling sequential circuits like flip-flops and registers, where updates should occur at the end of a clock cycle. This timing accuracy is critical for ensuring correct behavior in synthesized hardware.

2.2 Concurrency:

Parallel Execution: Non-blocking assignments allow multiple statements to execute concurrently within a clock cycle. This reflects the concurrent nature of real hardware, where different parts of a circuit can change states simultaneously.

2.3 Avoiding Race Conditions:

Consistent Updates: By deferring updates until the end of the time step, non-blocking assignments help prevent race conditions, where the order of operations could lead to unpredictable results.

2.4 Synchronized Behavior:

Clock Edge Sensitivity: Non-blocking assignments are ideal for modeling behaviors that need to synchronize with clock edges, ensuring that all updates occur simultaneously and consistently across all registers.

2.5 Simulation Accuracy:

Realistic Behavior: In simulations, non-blocking assignments provide a more accurate representation of how hardware behaves in real-world conditions, enhancing the reliability of the simulation results.

Disadvantages of Blocking and Non-blocking Assignments in Verilog Programming Language

1. disadvantages of blocking assignments, 1.1 potential for simulation issues:.

Unintended Dependencies: Since blocking assignments execute sequentially, they can inadvertently introduce unintended dependencies between statements, leading to potential issues in complex designs.

1.2 Limited for Sequential Logic:

Inaccurate Timing: Blocking assignments are not suitable for modeling sequential logic where updates should occur at specific clock edges, potentially leading to incorrect behavior in designs that rely on precise timing.

1.3 Race Conditions:

Concurrency Issues: When used in parallel processes, blocking assignments can lead to race conditions where the order of execution affects the final result, making it challenging to manage concurrent operations.

1.4 Complex Debugging:

Sequential Complexity: Debugging issues related to blocking assignments can be more complex, especially in designs with intricate sequential dependencies that affect the simulation outcomes.

2. Disadvantages of Non-Blocking Assignments

2.1 increased complexity:.

Understanding Concurrency: Non-blocking assignments introduce concurrency, which can make code more complex to understand and debug, particularly in designs with multiple interacting processes.

2.2 Potential for Unintended Behavior:

Delayed Updates: Since non-blocking assignments defer updates, there can be cases where intermediate values might not reflect changes as expected, potentially leading to unintended behavior in the design.

2.3 Less Immediate Feedback:

Deferred Results: Non-blocking assignments update variables at the end of the time step. This delay in updating may not provide immediate feedback, which can affect scenarios requiring instantaneous results.

2.4 Synthesis Challenges:

Complex Synthesis: While non-blocking assignments are essential for modeling sequential logic, they can sometimes complicate synthesis processes, especially if not used correctly, leading to inefficient hardware implementations.

Equivalent Technical Articles

Conditional Statements in C Programming

Do-While Loop In C Programming

While Loop in C Programming Language

- Digital Circuits

- System Verilog

- Design Verification

- Physical Design

- Interview Questions

- Informative

Blocking Vs Non-blocking Assignments in Verilog

Welcome to our article on blocking and non-blocking assignments in Verilog. In hardware description language (HDL) coding, these assignments play a crucial role in defining the behavior of circuits. Understanding the differences and implications of blocking and non-blocking assignments is essential for creating efficient and reliable hardware designs.

In this article, we will explore the syntax, functionality, and impact of blocking and non-blocking assignments on circuit behavior. We will discuss their usage in Verilog and provide best practices for incorporating these assignments into your code.

Whether you’re new to Verilog or looking to enhance your knowledge, this article will serve as a comprehensive guide to understanding the intricacies of blocking and non-blocking assignments. Let’s dive in and explore the fascinating world of Verilog assignments together!

Table of Contents

What are Blocking Assignments?

In Verilog, blocking assignments are a fundamental concept used to assign values to variables within hardware description language (HDL) coding. These assignments follow a sequential execution model, where statements are executed one after another in the order they appear in the code.

The syntax for a blocking assignment involves using the assignment operator (=) to assign a value to a variable. For example:

Here, the value of variable “a” is assigned as 2, and the value of variable “b” is assigned as the result of “a + 3”.

Blocking assignments have an immediate impact on the simulation and time delays within a hardware design. When a blocking assignment is encountered in the code, the next statement is not executed until the assignment is complete. This means that any subsequent operations will be delayed until the assignment is finished.

To better understand the concept of blocking assignments, let’s consider a simple circuit design example.

Suppose we have a circuit that consists of two flip-flops connected in series. The output of the first flip-flop is connected to the input of the second flip-flop. By using blocking assignments, we can model the sequential behavior of the flip-flops.

Below is a diagram depicting the circuit:

To implement this circuit in Verilog, we can use blocking assignments to update the values of the flip-flop outputs based on the inputs and current state. Here’s an example:

In this example, the values of “Q1” and “Q2” are updated sequentially using blocking assignments within the “always” block. When the “reset” signal is asserted, both flip-flops are reset to 0. Otherwise, the value of “Q1” is updated with the value of the “data” input, and the value of “Q2” is updated with the current value of “Q1”.

By using blocking assignments, we can accurately model the behavior of the circuit and ensure that the values of the flip-flops are updated in the correct order. This sequential execution is essential for correctly simulating the behavior of hardware designs in Verilog.

In the next section, we will explore non-blocking assignments in Verilog and understand how they differ from blocking assignments.

What are Non-blocking Assignments?

Non-blocking assignments in Verilog are a powerful concept that allows for modeling concurrent behavior in hardware description language (HDL) designs. Unlike blocking assignments, which execute sequentially and can cause delays in simulation, non-blocking assignments enable parallel execution and facilitate efficient modeling of digital circuits.

Non-blocking assignments are denoted by the “ <=” operator ” in Verilog. They are used to update the values of registers and variables in a non-blocking fashion, meaning that the assignments occur concurrently without any temporal dependencies. This allows for efficient scheduling and evaluation of operations within a digital design.

One key advantage of non-blocking assignments is their ability to model clocked behavior and simulate flip-flops and sequential elements accurately. By using non-blocking assignments, the values of these elements are updated simultaneously, capturing the concurrent nature of digital systems.

Let’s take a look at an example to illustrate non-blocking assignments:

“`verilog always @(posedge clk) begin a In this code snippet, the non-blocking assignments “

” ensure that the values of variables

are updated concurrently on the positive edge of the clock signal. This behavior accurately models the flip-flop operation where the output values are synchronized with the clock cycles. As a result, non-blocking assignments provide a more realistic representation of digital circuits.

When using non-blocking assignments, it is crucial to understand the behavior of race conditions, where multiple assignments occur simultaneously. Proper coding techniques and design practices can help prevent race conditions and ensure accurate circuit modeling.

Key Features of Non-blocking Assignments:

- Update variables concurrently

- Model clocked behavior accurately

- Synchronize flip-flops with clock cycles

- Enable efficient scheduling and evaluation

- Prevent race conditions with coding techniques

Non-blocking assignments have revolutionized the way digital circuits are represented and simulated in Verilog. Their ability to model concurrent behavior and accurately capture clocked operations makes them an essential tool for HDL designers.

Now that we have explored non-blocking assignments, let’s move on to the next section where we will compare the differences between blocking and non-blocking assignments in Verilog.

Differences between Blocking and Non-blocking Assignments

In Verilog, blocking and non-blocking assignments are two fundamental concepts that play a crucial role in hardware description language (HDL) coding. Understanding the differences between these assignment types is essential to ensure accurate and efficient circuit design. In this section, we will explore the key distinctions between blocking and non-blocking assignments, focusing on their behavior during simulation, race conditions, and impact on timing and concurrency.

Behavior during Simulation

Blocking assignments in Verilog follow a sequential execution model, where each assignment is executed one after the other. This means that a blocked assignment must complete before the next assignment in the same procedural block can begin. Consequently, changes made to variables within a blocking assignment immediately affect subsequent assignments.

On the other hand, non-blocking assignments allow concurrent execution within the same procedural block. This concurrent execution model permits all non-blocking assignments in the block to execute simultaneously, regardless of their order. The values assigned to variables are stored and updated at the end of the procedural block, ensuring that changes made within the block take effect in the next simulation cycle.

Race Conditions

Race conditions can occur when multiple processes or procedural blocks attempt to access and modify the same variable simultaneously. Blocking assignments are more prone to race conditions as they evaluate and update variables immediately, potentially leading to unpredictable results when multiple processes access the same variables concurrently.

Non-blocking assignments, on the other hand, are specifically designed to handle concurrency and avoid race conditions. By storing and updating values at the end of the procedural block, non-blocking assignments ensure that each process accesses the most recent value without interfering with other processes or creating race conditions.

Impact on Timing and Concurrency

The choice between blocking and non-blocking assignments can significantly impact timing and concurrency in circuit design. Blocking assignments introduce a delay in the circuit because each assignment must complete before the next can begin. This delay can affect the overall timing of the circuit, potentially leading to unintended delays or timing violations.

Non-blocking assignments, on the other hand, allow for parallel execution, improving overall concurrency and performance. By eliminating the need for sequential execution, non-blocking assignments enhance the efficiency of the circuit, enabling faster and more accurate simulation results.

It’s worth noting that the behavior of blocking and non-blocking assignments can differ depending on the context and the specific Verilog simulator being used. It is essential to understand the nuances and limitations of each assignment type to ensure reliable and predictable hardware designs.

As illustrated in the table above, the differences between blocking and non-blocking assignments can be summarized as follows:

Best Practices for Using Blocking and Non-blocking Assignments in Verilog

When working with Verilog assignments, it is important to follow industry best practices to ensure efficient and reliable hardware description language (HDL) coding. Whether you are using blocking or non-blocking assignments, adhering to these guidelines can significantly improve the quality and functionality of your designs. In this section, we will discuss essential considerations and recommendations for using blocking and non-blocking assignments effectively in Verilog.

Coding Style

Consistency in coding style plays a crucial role in Verilog assignments. It is recommended to adopt a standardized coding style that is easily understandable and maintainable by the entire development team. Here are some best practices:

- Use meaningful variable and signal names to enhance readability and comprehension.

- Follow proper indentation and formatting conventions to improve code organization.

- Document your code using comments to provide context and explanations.

- Avoid the use of magical or hard-coded values; use constants or parameters instead.

An example of well-structured and readable Verilog code:

“` module example_module( input wire clk, input wire reset, output wire reg result );

reg [7:0] counter;

always @(posedge clk or posedge reset) begin if (reset) begin counter

Timing Constraints

When using blocking and non-blocking assignments, it is crucial to consider timing constraints to ensure accurate behavioral modeling of the hardware design. Here are some recommendations:

- Understand the underlying clock and event relationships and apply them appropriately.

- Avoid excessive blocking assignments in synchronous sequential logic to prevent timing issues.

- Use non-blocking assignments in sequential logic to model concurrent updates effectively.

- Ensure proper synchronization and sequencing in your designs to avoid race conditions.

Avoiding Common Pitfalls

When working with Verilog assignments, it is essential to be aware of common pitfalls that can introduce bugs or reduce the overall efficiency of your code. Here are some tips to avoid these pitfalls:

- Avoid mixing blocking and non-blocking assignments within the same always block to maintain code clarity and prevent unintended side effects.

- Do not use blocking assignments in combinational logic to prevent simulation mismatches.

- Be cautious while using non-blocking assignments in control logic, as they may cause unexpected behavior.

- Verify signal dependencies and ensure proper sequencing to prevent race conditions and simulation mismatches.

- Utilize simulation and linting tools to detect potential coding errors and improve code reliability.

By following these best practices, you can enhance the efficiency, reliability, and understandability of your Verilog designs. Adhering to standardized coding practices and paying attention to timing constraints will contribute to the overall success of your projects.

In conclusion, understanding the differences between blocking and non-blocking assignments in Verilog is crucial for efficient HDL coding. Throughout this article, we have explored the syntax, functionality, and implications of these assignments, shedding light on their impact on circuit behavior.

Blocking assignments in Verilog provide a straightforward approach to sequential execution, where each statement is executed one after another. On the other hand, non-blocking assignments allow for concurrent behavior, enabling the simulation of multiple processes that can execute in parallel.

By grasping the distinctions between these assignment types, designers can accurately model and simulate hardware designs, considering factors such as timing, synchronization, and race conditions. By adhering to best practices and guidelines, developers can optimize their Verilog code and avoid common pitfalls along the way.

To delve deeper into Verilog and master the art of HDL coding, we recommend further exploring comprehensive resources such as online tutorials, textbooks, and specialized forums. These platforms provide invaluable insights, examples, and discussions that can enhance your understanding of Verilog assignments and enable you to create efficient and reliable hardware designs.

Related Posts

Assertions in verilog, verilog for rtl verification, verilog for rtl synthesis.

Save my name, email, and website in this browser for the next time I comment.

Type above and press Enter to search. Press Esc to cancel.

Blocking and Non-blocking Assignment in Verilog

- Assignment is only done in procedural block(always ot initial block)

- Both combintational and sequential circuit can be described.

- Assignment can only possible to reg type irrespect of circuit type

Let's say we want to describe a 4-bit shift register in Verilog. For this, we are required to declare a 3-bit reg type variable.

The output of shift[0] is the input of shift[1], output of shift[1] is input of shift[2], and all have the same clock. Let's complete the description using both assignment operator.

Non-Blocking Assignment

When we do synthesis, it consider non-blocking assignment separately for generating a netlist. If we see register assignment in below Verilog code, all register are different if we consider non-blocking assignment separately. If you do the synthesis, it will generate 3 registers with three input/output interconnects with a positive edge clock interconnect for all register. Based on the Verilog description, all are connected sequentially because shift[0] is assigned d, shift[1] is assigned shift[0], and shift[2] is assigned shift[1].

Blocking Assignment

If we use blocking assignment and do the syhtheis, the synthesis tool first generate netlist for first blocking assignment and then go for the next blocking assignment. If in next blocking assignment, if previous output of the register is assigned to next, it will generate only a wire of previously assigned register.

In below Verilog code, even though all looks three different assignment but synthesis tool generate netlist for first blocking assigment which is one register, working on positive edge of clock, input d and output shift[0]. Since blocking assignment is used, for next blocking assignment, only wire is generated which is connected to shift[0]. Same is for next statement a wire is generated which is connected to shift[0].

Click like if you found this useful

Add Comment

This policy contains information about your privacy. By posting, you are declaring that you understand this policy:

- Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice.

These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules:

- Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments.

These terms and conditions are subject to change at any time and without notice.

Comments (1)

hey in blocking assignment do we get shift in data i dont think so . we get all values same and equal to d.

Please do not focus on the module name; focus on how the netlist is generated after the synthesis.

News the global electronics community can trust

The trusted news source for power-conscious design engineers

Supply chain news for the electronics industry

The can't-miss forum engineers and hobbyists

The electronic components resource for engineers and purchasers

Design engineer' search engine for electronic components

Product news that empowers design decisions

The educational resource for the global engineering community

The learning center for future and novice engineers

The design site for electronics engineers and engineering managers

Where makers and hobbyists share projects

The design site for hardware software, and firmware engineers

Where electronics engineers discover the latest tools

Hardware design made easy

Brings you all the tools to tackle projects big and small - combining real-world components with online collaboration

Circuit simulation made easy

A free online environment where users can create, edit, and share electrical schematics, or convert between popular file formats like Eagle, Altium, and OrCAD.

Transform your product pages with embeddable schematic, simulation, and 3D content modules while providing interactive user experiences for your customers.

Find the IoT board you’ve been searching for using this interactive solution space to help you visualize the product selection process and showcase important trade-off decisions.

A worldwide innovation hub servicing component manufacturers and distributors with unique marketing solutions

SiliconExpert provides engineers with the data and insight they need to remove risk from the supply chain.

Transim powers many of the tools engineers use every day on manufacturers' websites and can develop solutions for any company.

Search EEWeb

- Newsletters

- Internal/External

- Embedded Microstrip

- Symmetric Stripline

- Asymmetric Stripline

- Wire Microstrip

- Wire Stripline

- Edge-Coupled Microstrip

- Edge-Coupled Stripline

- Broadside Coupled Stripline

- Twisted Pair

- RF Unit Converter

- Online SPICE Simulator

- Schematic Converter/Viewer

- Schematic Capture Tool

- Standard Values

- Magnetic Field Calculator

- Wire Self Inductance

- Parallel Wires

- Wire over Plane

- Rectangle Loop

- Broadside-Coupled Traces

- Edge-Coupled Traces

- Engineering Paper (Printable PDF)

- Log-Log Graph Paper (PDF Download)

- Semi-Log Graph Paper (PDF Download)

- Smith Chart Graph Paper (PDF Download)

- Math Reference Sheets Overview

- Algebra Reference Sheet

- Geometry Reference Sheet

- Trigonometry Definitions and Functions

- Trigonometry Rules, Laws, and Identities

- Calculus Derivatives, Rules, and Limits

- Calculus Integrals Reference Sheet

- Online Basic Calculator

- Scientific Calculator

- Tech Communities

- Analog Design

- Power Design

- Digital Design

- Embedded Systems

- Test & Measurement

- Electromechanical

- Passive Components

- Design Library

- Extreme Circuits

- Magazines Archive

- Design Contest

Verilog Blocking vs Non-Blocking Assignments

In writing verilog one of the common misunderstandings is the difference between a blocking and a non-blocking assignment. Explain the difference and the syntax used with these assignments?

There are synthesis differences between a blocking statement and a non-blocking statement.

Blocking Assignment

The syntax for a blocking assignment is:

always @ (pos edge clk) begin x=y; y=z; end

In this blocking assignment immediately after rising transition of the clk signal, x=y=z.

Non-Blocking Assignment

The syntax for a non-blocking assignment is:

always @ (pos edge clk) begin x<=y; y<=z; end

In this non-blocking assignment immediately after rising transition of the clk signal, x=y and y=z, but x!=z. Synthesis for this code would typically create a register for x and a register for y. Where blocking assignments often are synthesized as logic.

Other Related Topics

- Photonic Device as Miniature Toolkit for Measurements

- 3D Print Prototype for ‘Bionic Eye’

- Glass Data Storage

- Biodegradable, Paper-based Biobatteries

Join the Conversation!

Add comment cancel reply.

You must be logged in to post a comment.

This site uses Akismet to reduce spam. Learn how your comment data is processed .

- FarhnSh1d 2024-04-03 02:40:00 1. Energy Source Availability: Identify available energy sources such as solar, wind, vibration, thermal gradients, or ambient RF signals. Choose a technology capable of effectively capturing and converting this energy into usable electrical power. 2. Energy Density and Power Output: Assess the energy density and power output of each potential source to determine if it can meet the application's power requirements, considering factors like sensor power consumption and duty cycle. 3. Environmental Conditions: Evaluate the environmental conditions of the remote location, including temperature extremes, humidity, and exposure to elements. Choose a technology that can withstand these conditions and operate reliably...

- FarhnSh1d 2024-04-03 02:39:02 Reducing the output power of an ultrasonic Piezo Ceramic disc from 35 watts to 10 watts by adjusting the control board is possible but entails several considerations: Effectiveness and Performance Lowering power may compromise the effectiveness of the ultrasonic device, potentially reducing its ability to achieve desired results like cleaning or atomization. Reduced power might lead to weaker vibrations, impacting performance, especially if the device operates away from its optimal resonance frequency. Durability and Lifespan Lowering power could potentially increase the device's lifespan by reducing stress on the piezo ceramic disc. However, extreme power reductions may lead to inadequate vibrations...

- forlinxembedded 2024-03-21 04:05:55 Hello Erdem, It's interesting to learn about the differences in electric pole usage between countries. In many countries, wooden poles are commonly used due to their availability, cost-effectiveness, and ease of installation. However, in regions with higher load requirements like Turkey, stronger poles are necessary to support the infrastructure. In the USA and some European countries, wooden poles are reinforced and treated to withstand the required loads. Additionally, alternative materials like steel and concrete are also used for electric poles in various applications. If you're interested in learning more about electric pole types and standards in different countries, I recommend...

- Lumispot 2024-03-04 11:00:10 Microcontroller For a project like yours, the choice of a microcontroller (MCU) largely depends on the complexity of the device, the number of input/output peripherals you need (like GPIOs for the sensor, speaker, LED lights, and the green light indicator), and any additional features you might require (such as PWM outputs for LED dimming or speaker volume control). Arduino Uno is a robust choice for beginners and prototypes. It's based on the ATmega328P and offers a good balance of GPIO pins, is easy to program, and has extensive community support. Arduino Nano or Arduino Micro could be more suitable for...

- richard-gabric 2024-03-04 11:00:01 You are setting yourself up to kill yourself, or at least to take an eye out. You don't say what DC voltage you need, the voltage you would get from directly applying the mains to a bridge rectifier were typically used, for example, to supply the input to a flyback switch mode power supply, where the switching transformer provides mains isolation. The voltage would typically be around 300V DC, and the rectifier and capacitors have to be rated for that voltage plus a safety factor. I assume that you are needing a low voltage DC, since you have 25Vdc capacitors...

- suvsystemltd 2024-03-01 09:15:42 one suitable device is the LTC4371 from Analog Devices. The LTC4371 is an automotive-grade ideal diode controller designed to operate in harsh environments, making it compliant with the AEC-Q100 standard. Key features of the LTC4371 include: Input Voltage Range: The LTC4371 typically operates with an input voltage range that covers your specified 2.5V requirement. AEC-Q100 Qualification: The LTC4371 is qualified for automotive applications, meeting the AEC-Q100 standard. This ensures reliability and performance under automotive operating conditions. Ideal Diode Functionality: The LTC4371 is specifically designed as an ideal diode/OR-ing controller. It allows for seamless power source transition and provides a low-loss...

- AdeZep 2024-02-23 07:14:54 74AC14 willl do the job ? Thanks!...

- ViasionTech 2024-02-13 09:30:44 In the USA and parts of the EU, wooden electric transmission poles are commonly used due to their cost-effectiveness, widespread availability, and environmental friendliness. The decision is influenced by regional engineering standards, emphasizing factors like renewable resources and biodegradability. While wooden poles may have lower load-bearing capacity than those used in Turkey, they meet safety requirements for specific voltage and environmental conditions. To obtain detailed information about electric pole types and standards in a specific country, it is advisable to contact local electric utilities, government agencies, or industry associations for relevant documentation or standards....

Browse by Categories

- Amplifiers (52)

- Analog Design (139)

- Digital Design (63)

- Diodes, Transistors and Thyristors (44)

- General (82)

- Passive Components (45)

- Power Design (90)

- Power Management (44)

- RF Design (102)

- RF and Microwave (50)

- Test & Measurement (37)

- Uncategorized (125)

Browse by Topics

- Amplifiers (58)

- Circuits (32)

- Current (41)

- Electronics (44)

- Transmission Line (25)

- Voltage (39)

- List of Topics

Blocking (immediate) and Non-Blocking (deferred) Assignments in Verilog

There are Two types of Procedural Assignments in Verilog.

- Blocking Assignments

- Nonblocking Assignments

To learn more about Delay: Read Delay in Assignment (#) in Verilog

Blocking assignments

- Blocking assignments (=) are done sequentially in the order the statements are written.

- A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed.

Non-Blocking assignments

- Nonblocking assignments (<=), which follow each other in the code, are started in parallel.

- The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure.

- The transfer to the left hand side is made according to the delays. An intra- assignment delay in a non-blocking statement will not delay the start of any subsequent statement blocking or non-blocking. However normal delays are cumulative and will delay the output.

- Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time.

To learn more about Blocking and Non_Blocking Assignments: Read Synthesis and Functioning of Blocking and Non-Blocking Assignments

The following example shows interactions between blocking and non-blocking for simulation only (not for synthesis).

For Synthesis (Points to Remember):

- One must not mix “<=” or “=” in the same procedure.

- “<=” best mimics what physical flip-flops do; use it for “always @ (posedge clk..) type procedures.

- “=” best corresponds to what c/c++ code would do; use it for combinational procedures.

Spread the Word

- Click to share on Facebook (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on LinkedIn (Opens in new window)

- Click to share on Pinterest (Opens in new window)

- Click to share on Tumblr (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to share on Reddit (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

Related posts:

- Synthesis and Functioning of Blocking and Non-Blocking Assignments.

- Delay in Assignment (#) in Verilog

- Ports in Verilog Module

- Module Instantiation in Verilog

Post navigation

Leave a reply cancel reply.

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Notify me of follow-up comments by email.

Notify me of new posts by email.

Verilog Blocking & Non-Blocking assignments elaborated

- Post author By Kevin

- Post date 20 October 2020

Blocking / Non-Blocking assignment rules

The main reason to use either Blocking or Non-Blocking assignments is to generate either combinational or sequential logic.

In non-blocking assignments (<=), all registers inside the always block are updated at the end. In blocking assignments (=), the registers are updated immediately.

Whether or not a flip-flop is inferred from a blocking assignment depends on whether or not the value of the variable being assigned needs to be remembered from one clock edge to the next.

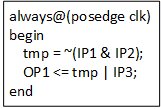

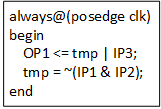

It is good practice to separate combinational and sequential code as much as possible. In verilog, if we want to create sequential logic can use a clocked always block with non-blocking assignments. If on the other hand we want to create combinational logic can use an always block with blocking assignments. Best not to mix the two in the same always block but if they are mixed, need to be careful when doing this. Its up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a flip-flop or not. If the signal is read before being assigned (eg fig2 below), the tools will infer sequential logic.

For simplicity purposes only showing in the verilog examples below the Always Block. These Always blocks are blocks of sequential logic since it involves a clock.

If on an active clock edge, the variable tmp is being assigned a value before it’s value is used (ie ‘write before read’ case) then no flip-flop is required & synthesis will not infer it as shown in fig1 below.

If the value of the reg is used before a new value is assigned to it (ie ‘read before write’ case), then the value that is used will be the value that was assigned on a previous clock. Therefore a flip-flop is required here as shown in fig2 below.

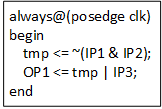

If all non-blocking assignments are used within the always block, it will look like :

Non-blocking assignments always imply flip-flops (order of assignments doesn’t matter). Same block diagram is inferred on both cases as shown in fig3 above. They result in simultaneous or parallel statement execution.

- Verilog Tutorial

- Lexical Tokens

- ASIC Design Flow

- Design Abstraction Layers

- Verilog Data Types

- Behavioral Modelling & Timing

- Verilog Module

- RTL Verilog

- Scalar & Vector

- Verilog Arrays

- Verilog Port

- Assign Statements

- Verilog always Block

- Verilog Initial block

- Verilog Block Statements

- Verilog Assignment

- Blocking & Non-blocking

- Verilog Control Blocks

- Verilog Functions

- Verilog Task

- Verilog Case Statement

- Verilog Parameters

- Verilog Timing Control

- Inter & Intra Delay

- Verilog Gate Delays

- Data Flow Modeling

- Gate Level Modeling

- Switch Level Modeling

- User Defined Primitives

- Verilog Simulation Basics

- Verilog Timescale

- Verilog Timeformat

- Scheduling Semantics

- Verilog Display Tasks

- JK Flip Flop

- D Flip-Flop

- T Flip Flop

- Verilog D Latch

- Ripple Counter

- Ring Counter

- 4-bit Counter

- Mod-N Counter

- Johnson Counter

- Bidirectional Shift Register

- Gray Counter

- File Operations

- Verilog Full Adder

- Priority Encoder

- Verilog Multiplexer

Latest Courses

We provides tutorials and interview questions of all technology like java tutorial, android, java frameworks

Contact info

G-13, 2nd Floor, Sec-3, Noida, UP, 201301, India

[email protected] .

Latest Post

PRIVACY POLICY

Interview Questions

Online compiler.

IMAGES

VIDEO

COMMENTS

The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step. Simulation Log. ncsim> run. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx.

I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and assignment are immediate • Nonblocking assignment: all assignments deferred until all right-hand sides have been evaluated (end of simulation timestep)

was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed. Non-blocking assignment ...

Blocking vs. Nonblocking in Verilog. The concept of Blocking vs. Nonblocking signal assignments is a unique one to hardware description languages. The main reason to use either Blocking or Nonblocking assignments is to generate either combinational or sequential logic. In software, all assignments work one at a time. So for example in the C ...

In Verilog, blocking and non-blocking assignments determine how variables receive values and manage the execution of statements within procedural blocks. These assignments play a crucial role in modeling and simulating digital circuits, ensuring that your designs perform as intended. 1. Blocking Assignments.

Differences between Blocking and Non-blocking Assignments. In Verilog, blocking and non-blocking assignments are two fundamental concepts that play a crucial role in hardware description language (HDL) coding. Understanding the differences between these assignment types is essential to ensure accurate and efficient circuit design.

The conventional Verilog wisdom has it all wrong. There is no problem with using blocking assignments for a local variable. However, you should never use blocking assignments for synchronous communication, as this is nondeterministic. A non-blocking assignment within a clocked always block will always infer a flip-flop, as dictated by the ...

4. The blocking vs non blocking assignment is a crucial concept and you have difficulty to implement them correctly because you have not understood the conceptual difference. I have attached a slide of MIT OCV PowerPoint lecture, 2005, that clearly describe the difference between the two.

When working with behavioural modeling in Verilog, there are two types of assigment which is known as blocking and non blocking assigment and both of them there is a operator, '=' operator for blocking assignment and '<=' operator for non blocking assigment. At short, blocking assignment executes one by one sequentially and non-blocking ...

Non-Blocking Assignment. The syntax for a non-blocking assignment is: always @ (pos edge clk) begin x<=y; y<=z; end. In this non-blocking assignment immediately after rising transition of the clk signal, x=y and y=z, but x!=z. Synthesis for this code would typically create a register for x and a register for y. Where blocking assignments often ...

Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time. Example: module Non_Blocking(. input a, // Assume a=1 initialized at time '0'.

Blocking vs Non-Blocking Cont • Non-blocking assignments literally do not blockthe execution of the next statements. The right side of all statements are determined first, then the left sides are assigned together. - Consequently, non-blocking assignments result in simultaneous or parallel statement execution. For example: assume a = b = 0 ...

This page contains tidbits on writing FSM in verilog, difference between blocking and non blocking assignments in verilog, difference between wire and reg, metastability, cross frequency domain interfacing, all about resets, FIFO depth calculation,Typical Verification Flow

end. There are now two extra states and an else. The else is needed because two dependent blocking assign-ments happen in the first clock cycle, except when the input is 2. In that case, there is only one assignment (of the input to the output). As discussed earlier, equiva-lent non-blocking code requires an if else.

An edge-sensitive intra-assignment timing control permits a special use of the repeat loop. The edge sensitive time control may be repeated several times before the delay is completed. Either the blocking or the non-blocking assignment may be used. always always @(IN) @(IN) OUT OUT <= <= repeat.

20 October 2020. Blocking / Non-Blocking assignment rules. The main reason to use either Blocking or Non-Blocking assignments is to generate either combinational or sequential logic. In non-blocking assignments (<=), all registers inside the always block are updated at the end. In blocking assignments (=), the registers are updated immediately.

Verilog supports blocking and non-blocking assignments statements within the always block with their different behaviors. The blocking assignment is similar to software assignment statements found in most popular programming languages. The non-blocking assignment is the more natural assignment statement to describe many hardware systems ...

I understand that blocking assignments execute in a sequential manner,whereas it is possible to assign values concurrently using non-blocking statements. My question is, why was non-blocking assignments included in Verilog. I can think of the following example to give weight to my statement. Using blocking assignment:

Non-blocking assignments were created to help model sequential logic. They help distinguish between the old and new value of a signal. They should be avoided in combinatorial logic as they can create problems with simulation if there are multiple clock domains. It also creates a lot of unnecessary signal rippling.

Verilog "blocking vs. non-blocking" assignments and simulation timestep meaning. General rule of thumb: Use blocking (=) in always_comb type blocks modeling combi logic. Use non-blocking (<=) in always_ff type blocks to model sequential logic. My question is when describing how the RHS/LHS (right hand/left hand side) of an assignment is ...